# WaveFormer Pro/VeriLogger Pro と アジレント社ロジックアナライザ/パターンジェネレータ による 設計と実機デバッグの統合による効率改善

従来、だれもが不便とは感じながらも、設計時のデータを実機デバッグに、実機データを設計に<u>効率的に役立てる汎用的な方法</u>はあまり普及していませんでした。SynaptiCAD社はアジレント社の協力をえてこの問題を解決しました。アジレント社のロジックアナライザ/パターンジェネレータとSynaptiCAD社のWaveFormer Pro/VeriLogger Proとのファイル互換を実現するインターフェースをとり、必要とされる機能を追加して、設計と実機デバッグの(両方向の)橋渡しを実現しました。

この機構の運用は、ユーザごとに多様に考えられると思いますが、以下に代表的な運用例を示します。

### (運用例)

- 1) ロジアナからのデータをシミュレータのスティミュラスに (VHDL、Verilog Abel Altera-AHDL...)

- 2) シミュレータの入力波形をパターンジェネレターで、実機への入力信号に変換 シミュレータの出力波形は期待値として、ロジアナでサンプリングした複数信号と一括自動比較

- 3) ロジアナからのデータのsetup/hold一括タイミングチェック

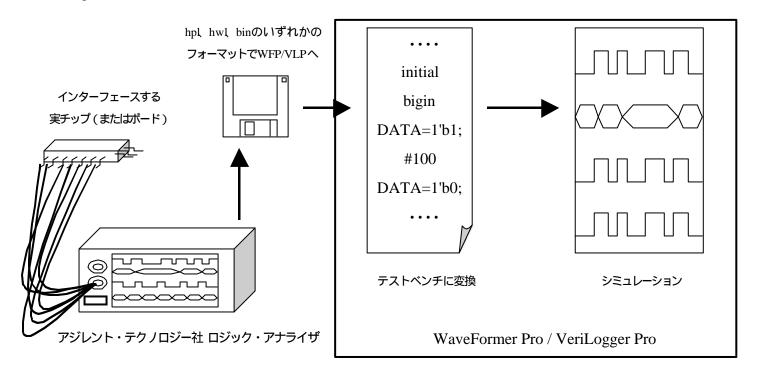

# 1.ロジックアナライザからのデータをシミュレータのスティミュラスに インターフェースするチップや装置の信号をテスト・ベクタとして利用

複雑なインターフェース仕様やプロトコル仕様を持つチップや装置を開発する場合、シミュレーション用の テスト・ベクタの準備が大きな負担となります。実際に稼働している接続されるチップや装置が存在している のであれば、これらからの信号をロジアナでサンプリングして、Waveformer Pro/VeriLogger ProでVHDL、 Verilog、Abel、Altera-AHDLなどの形式のテスト・ベクタに変換して設計に使用することができます。

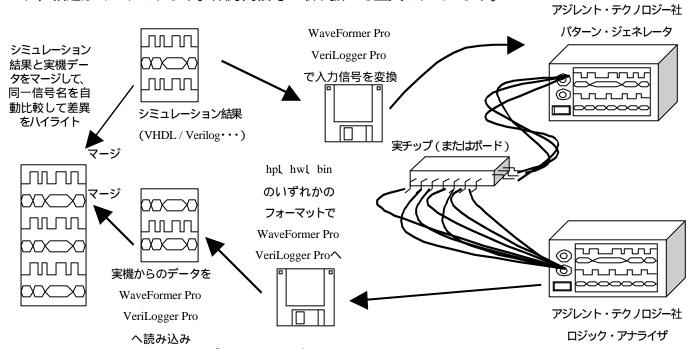

### 2.シミュレーション結果の波形データを実機のデバッグに再利用する シミュレータの入力波形をパターンジェネレターで、実機への入力信号に変換 出力波形は期待値として、ロジアナでサンプリングした複数信号と一括自動比較

不具合がなければ、設計モデルと実機は同じ動作を示すはずです。シミュレーション結果をWaveformer Pro/VeriLogger Proに読み込みます。例えばVerilogシミュレーションであれば一がをVCDフォーマットにしてWaveFormer Proで読み込みます。 VeriLogger Proは自身がVerilogシミュレータでもあるので、 VeriLogger Pro上でのシミュレーションであればこの作業は必要ありません。

入力信号はアジレント社パターンジェネレータのフォーマットに変換され実機の入力信号とされ、出力信号はアジレント社ロジアナでサンプルされた実機の出力と、設定されたトレランスを考慮の上で一括自動比較され、相違がマークされます。双方向信号の取り扱いも工夫されています。

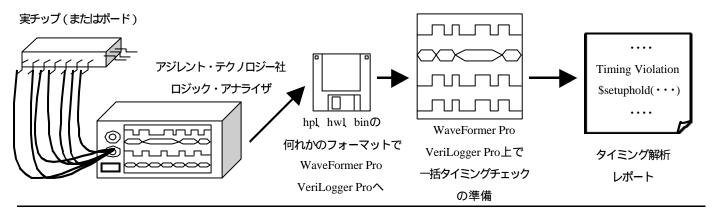

# 3.ロジアナでサンプルしたデータのsetup/hold一括タイミングチェック クリチカルパスの実機テストに 間欠的に起こる問題の解析に

ロジアナで、レジスタ・データなどタイミング制約を受けている信号とタイミング制約の基準となる信号(クロックやコントロール信号)を同時にサンプリングし、Waveformer Pro/VeriLogger Proに読み込みます。信号間の制約条件を付加して、内部に検査用のVerilogモデルを構築してWaveformer Pro/VeriLogger Pro のもつVerilogシミュレーション・コアに渡して、サンプリングした範囲の一括検査を行います。

**InterLink** 有限会社 インターリンク 231-0048 横浜市中区蓬莱町2-6-2 208 TEL:045-262-3960 FAX:045-262-3965 e-mail:sales@ilink.co.jp http://www.ilink.co.jp