# **SynaptiCAD**

# WaveFormer Pro

タイミング編集 / タイミング解析 / インターラクティブVerilogシミュレーションと スティミュラスの自動生成機能を持つ新しいツール

VHDL, Verilog, Abel, Altera, Spice, VCD, HP/Tekロジアナ&パターンジェネレータ, TDML, STIL, etc...

回路を設計するとき、HDLを使うにしるゲート・レベルにしるシミュレータでの検証やタイミング解析抜きにはASICや高速高密度のPCBの設計はできません。しかしシミュレータに与えるテスト・スティミュラスの準備はきわめて面倒な作業で、テストに十分なセットが用意できなかったリドキュメントが不備なままなど、いろいろとおろそかになりがちです。またゲート・レベルや標準部品での設計や検証のときのタイミングの解析も、紙の上では描いたり消したりで間違えやすく、そのドキュメントの管理と維持に困難をきわめます。このような波形に関する電子回路設計に伴う問題を、一挙に解決するために用意されたのが、WaveFormerProです、Verilogシミュレータのコアを内在しているので複雑な波形の生成や、インターラクティブ・シミュレータとしての応用も可能でユーザの工夫で多岐にわたる運用が可能です。

# WaveFormerProの概要

WaveFormerProはタイミング・ダイアグラムの編集/解析機能とテスト・スティミュラスの自動生成機能を合わせ持っている最新のローコストEDAツールです。タイミング・ダイアグラムのエディタは、デジタル回路のタイミング・ダイアグラムの作成と解析に使われる、比較的新しいツールです。テスト・スティミュラスの自動生成機能には、シミュレータやATEに与える色々なフォーマットのテスト波形の生成、取り込み、変換の機能が含まれます。これらの機能を一つの製品に組み込むことにより、WaveFormerPro はタイミング・ダイアグラムの生成と解析、そしてデジタル信号波形のドキュメント化のための統合された環境を提供します。標準でサポートする bitmap、postscript、VHDL、Verilog、HDL、Spiceなどのフォーマット以外にもPerl言語をベースとする組み込みスクリプト言語によるプログラミングでどんな波形フォーマットも生成できます。

## なぜタイミング・ダイアグラム・エディタは必要か?

タイミング・ダイアグラムは波形動作から回路を見た、デジタル回路の別の表現です、ひとつのタイミング・ダイアグラムには、ディレイ、セットアップ、ホールドなどのパラメータによる信号遷移にもとずく回路の因果関係が示されており、タイミング解析をWaveFormerProにより正確に行うことにより、次の利点がえられます。

システムの検証/解析を回路を設計する以前にも行うこともできます-

シミュレータは回路の設計後にしか使えませんが、タイミング・ダイアグラムの検証/解析はデバイスのデータブックに記載されているタイミング・パラメータのみで行え、回路のネットリストやシミュレーション・モデルを必要としません.

例えデジタル・シミュレータが使えたとしても、設計条件の厳しい部分の動作を把握するためにタイミング・ダイアグラムを描くことは必要です、この作業をきわめて容易にしてくれます。

タイミングの計算は対話的に行え、WaveFormerProのパラメータ・スプレッド・シートを通してのタイミング・パラメータを変化させることにより、その場でそのパラメータの変更の影響を即座に評価できます。これはLotus123やExcelでのシミュレーションに似ています。これにより不必要に高速な部品の使用を排除でき、PCBのコストダウンができます。周波数を変化させてシミュレーション(スプレッドシート)することにより回路の最高動作周波数がわかります。

タイミング・ダイアグラムは回路図やHDLのソースリスト同様に重要な設計ドキュメントです.これを正確に維持・管理することは大変に重要ですがWaveFormerProを設計,デバッグを通して使用することにより自然に実行できます.

シミュレータやATEに与えるテスト・データをHDLや装置固有の言語で記述することは大変間違えやすく,また非効率な作業です.これは視覚的な補助のもとに行われるべきです.

## タイミング編集 - わかりやす〈簡単な操作でのタイミング・ダイアグラムの描画と編集

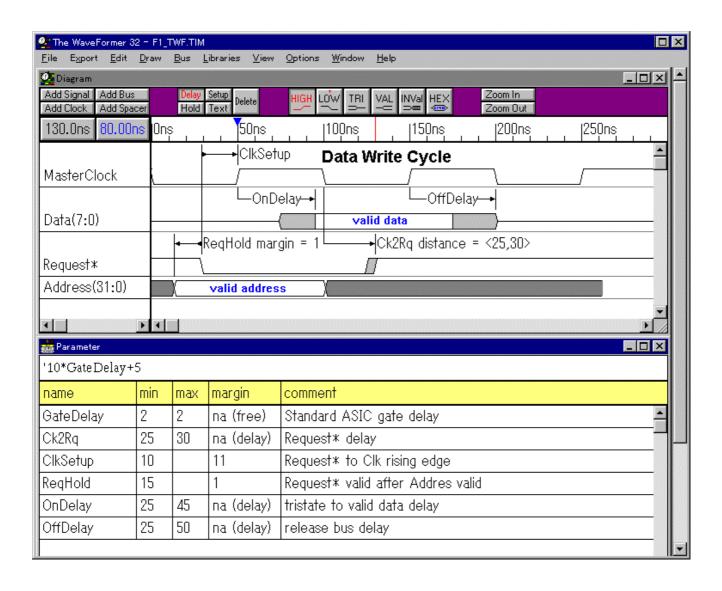

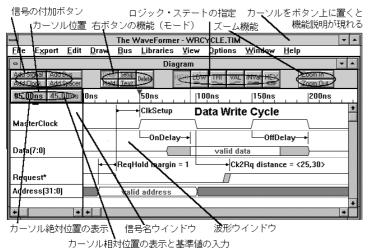

図1にダイアグラム・ウインドウ上の操作ボタンの様子をしめしました. ほとんどの描画が,この機能別に分類されたボタン群の操作だけでできるようになっています.

図1:ダイアグラム・ウインドウとボタンの役割の説明

## 信号の付加,名前,移動

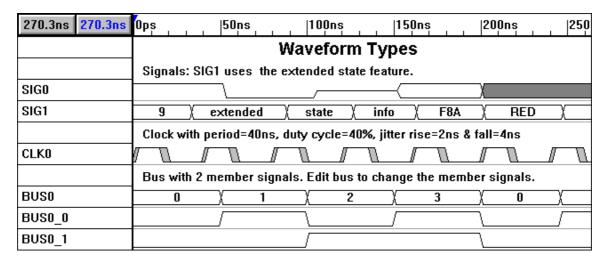

信号の付加 - WaveFormerProは信号,バス,クロックを波形の絵で示します.図2はこの3種の異なった波形を示しています.それぞれツール・バーの左上角の信号の付加ボタンのグループから,対応する信号の付加ボタンを左クリックすることにより生成されます.

図 2: WaveFormerProの生成する信号,クロック,バスの3種類の信号種

## 波形セグメントの編集

オブジェクト指向的な考えの,統一された判りやすい,マウス操作回数の少ない効率的方法で波形セグメント(一つの信号遷移と次の信号遷移まで)の描画と編集ができます.はじめ目盛りを参考に相対的に正しい描画をし,必要に応じて正確な値を数値で指定し直すことによりすばやい描画と編集ができます.

後からの,ロジック・ステートの変更,遷移時間の変更,波形セグメントの挿入/消去,なども自由自在に簡単な操作で可能です.時間間隔の計測もすばや〈正確に行えます.

### バス波形

バスは信号を束ねたもので,あたかも一つの信号のように便宜的に扱うものです.バスの値は要素の信号の持つロジック・ステートを反映した値を表示します.バスまたは要素の信号のうちどちらかが変化したなら,他方も対応するアップ・デートが起こります.バスのセグメントへのステート値の入力は,構成要素の信号の波形を自動生成するので,バスとして扱うことにより時間を大いに節約できす.ステート値の入力は16進でも2進でも入力可能です.

## クロック波形

クロックは周期性を持つ特別な信号で、周期(または周波数)、デューティ・サイクル、エッジ・ジッタなどのクロック固有のアトリビュートを設定することにより自動生成されます、クロックに関するアトリビュートには他のクロックのタイミング・パラメータの参照をふくむ式を指定可能です・例えば(CLK1.period = CLK0.period / '2).これにより、クロック分周やPLL周波数ジェネレータなどが簡単にモデリングできます。

クロックのアトリビュートの変更は何時でも行え,例えば周波数を変えることにより動作可能な最高周波数を求めることができます.

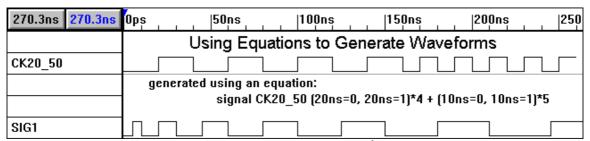

### 式による波形の生成

信号によっては,時間規定を式で指定したほうが,個々の波形セグメントをマウスで描画するより適した場合があります.

例1) 25MHzを4周期後50Mhzを5周期の波形を持つ信号CK25\_50の生成をWaveFormerProに指示する場合は下記の式で表現でき、図3上の波形を生成します.

```

CK25_50 (20ns=0 20ns=1)*4 (10ns=0 10ns=1)*5

```

尚,(20ns=0 20ns=1)\*4 は,20ns間のステート値0と20ns間のステート値1周期としこれを4回繰り返すという意味です.

- 例2) この波形を式で入力できる機能と、時間とステート値が変数に使えるWaveFormer Pro のスクリプト言語処理機能とが合わさると、きわめて複雑な波形の生成が可能になります、例えば、だんだんに周波数が小さくなる図3下の波形の生成(100Mhzから10Mhzへ)は以下の簡単なスクリプトで可能です。

- \* Perl言語とVerilog-HDL言語による方法があります、下記の例はPerl言語による例、

図3: 式による信号CK20 50波形の生成とスクリプトによるSIG1の波形の生成

## タイミング解析 - 遅延,,セットアップ・タイム,ホールド・タイムによるパラメータ解析

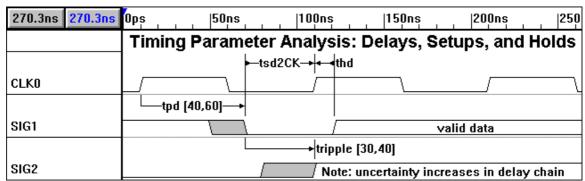

タイミング・ダイアグラム・エディタの真価はタイミング・パラメータを通しての異なる信号遷移間の関連付けにあります、WaveformerProは3つの基本的なタイミング・パラメータの型である遅延時間,セットアップ・タイム,ホールド・タイム(図4)を最大値,最小値などの幅をもたせて波形に条件付けすることが,ダイアグラム・ウインドウでの遷移位置の指定,パラメータ・ウインドウでのパラメータ名と数値の代入による簡単な操作でできます.

セットアップ・タイムとホールド・タイムは,システムが正常に働くために合致しなければならないタイミングの制約です.これらの制約条件の監視も行い,マージンを計算し不足に対してはダイアグラム・ウインドウ,パラメータ・ウインドウ(図5)とも該当個所を赤色で警告するので問題の箇所がすばやく発見できます.

図4: タイミング解析 - 遅延時間は遷移の時間差を, セットアップとホールドは遷移の時間差の制約

WaveFormerPro は自動的にこのマージンを計算しスプレッドシートに表示するので,設計者はこれをもとに,必要にして十分な余裕になるように回路のタイミングの調整ができます.全てのマージンがタイミングの変更のつどすぐに自動的に計算し直され,その場に結果が表示される(スプレッドシート機能)ので,色々な試みをシミュレーションでき,回路を最適なものにできます.タイミング・パラメータは数値の直接代入ではなく,変数やマクロ変数として持たせることもでき,多く同じ値を使う場合や,プロセスやデバイス・ファミリの変更に柔軟に対応でき,同一のダイアグラムが使用できます.また WaveFormerProには多くの標準ロジック・デバイスのタイミング・ライブラリがオプションで用意されており,これを使うことで標準ロジック・デバイスを使用する場合はデバイスの選択だけでタイミング解析ができます.他にインテルのCPUのモデルもあります.

| 0               | Parameter |     |            |                                   |     |

|-----------------|-----------|-----|------------|-----------------------------------|-----|

| '10*GateDelay+5 |           |     |            |                                   |     |

| name            | min       | max | margin     | comment                           |     |

| GateDelay       | 2         | 2   | na (free)  | Standard ASIC gate delay          | +   |

| Ck2Rq           | 25        | 30  | na (delay) | Request* delay                    | 100 |

| ClkSetup        | 10        |     | 11         | Request* to Clk rising edge       |     |

| ReqHold         | 15        |     | 1          | Request* valid after Addres valid |     |

| OnDelay         | 25        | 45  | na (delay) | tristate to valid data delay      |     |

| OffDelay        | 25        | 50  | na (delay) | release bus delay                 |     |

|                 | •         | •   | •          | •                                 | +   |

図5: パラメータ・ウインドウは、パラメータのスプレッドシート機能をもちます

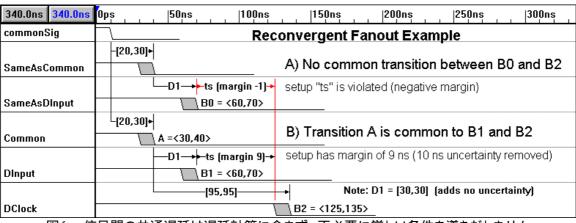

WaveFormerPro は信号間の遅延の計算において、パスの共通部分を認識し、共通部分の遅延(図6)はタイミング計算に取り込まず、信号が分かれた所から計算を始めます、これにより、不必要に厳しい条件を導き出しません。

図6: 信号間の共通遅延は遅延計算に含まず,不必要に厳しい条件を導きだしません

# <u>スティミュラス生成機能 - VHDL, Verilog-HDL, Viewsim, Spice, Abel, Altera</u> HPパターン・ジェネレータ、STILテスタ・フォマット

WaveFormerProはタイミング編集機能を使いスティミュラスをグラフィカルにもテキスト記述にてでも生成でき、シミュレータの上でなくその場で視覚的に確認できます.一つのスティミュラスを表すWaveFormerPro上の波形から色々なフォーマットのスティミュラスが生成可能す. WaveFormerProはVHDL, Verilog-HDL, SPICE, Viewsim (Viewlogic)の形式のテスト・スティミュラスを標準でサポートしていますが、任意のフォーマットがスクリプトを書くことにより生成されるので、シミュレータ以外にも任意のATEへのテスト・ベクタの準備などの用途もあります.

## 簡単なスティミュラス生成例

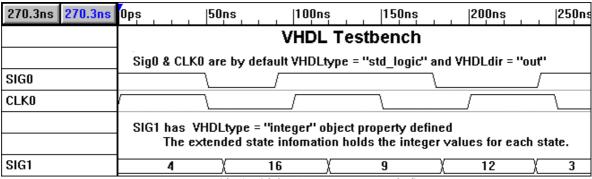

WaveFormerProはVHDL, Verilog, Spice, そしてユーザによる変換スクリプト・プログラムにより独自のフォーマットさえ読み込みまたは書き出しができます。ここでは書き出しの例として, WaveFormerProに標準として用意されている"VHDL transport"スクリプトによる,信号遷移をVHDLシンタックスの処理信号代入文で置き換える例を示します。このスクリプトは完全なentity-architectureの構造を含むテスト・ベンチを生成し直接コンパイル,リンクできVHDLシミュレータに直接もって行けます。

VHDLで許される複雑なデータ型のモデル化のため、"VHDL transport"スクリプトはWaveformerProのオブジェクト・プロパティと拡張されたステートを使用します.これらの機能により、"VHDL transport"スクリプトがVHDLコードの生成に必要な情報をタイミング・ダイアグラムの信号オブジェクトに付加できます.

図7bはWaveFormerProに含まれる"VHDL transport"スクリプトを使い図7aより得られたものです.

図7a: 波形に対応したVHDLコードの生成

```

library ieee, std;

use std.textio.all;

process

use ieee.std logic 1164.all;

begin

SIG0 <=

entity testbench is

transport '1' after 0 ps,

transport '0' after 50000 ps,

port(

transport '1' after 90000 ps,

SIG0

: out std_logic;

CLK0

: out std logic;

transport '0' after 180000 ps,

SIG1

: out integer

transport '1' after 240000 ps;

SIG1 <=

):

end testbench;

transport 4 after 0 ps,

transport 16 after 60000 ps,

architecture test of testbench is

transport 9 after 120000 ps,

begin

transport 12 after 185000 ps,

transport 3 after 238000 ps;

process

end process;

begin

CLK0 <= '1';

end test;

wait for 0 ps;

while true loop

CLK0 <= '0';

wait for 50000 ps;

CLK0 <= '1':

wait for 50000 ps;

end loop;

end process;

```

図7b: WaveFormerProにより生成されたVHDLコード

## 波形フォーマット変換と独自のフォーマットのサポート

WaveFormerProは他のツールの波形データを取り込むこともでき、異なる波形フォーマット間のトランスレータとしての利用することもできます。現在のバージョンでは、VCD、Accolade VHDL、ViewSim、HPロジアナ、Pod-A-Lyzer(PCベースのロジック・アナライザ)の波形データを標準で取り込むことができます。これには、サポートされたここのツールに対する便宜だけでなく、色々おもしろい運用が考えられます。例えばAccolade VHDLシミュレーを通してVHDL言語を波形生成に利用したり、Pod-A-Lyzerから現機種のデータをとり新機種のためのテスト・スティミュラスに利用したりなど色々な用途が開けます。ステミュラス生成だけでなく、入力においてもスクリプト・プログラムにより任意のフォーマットが取り込めるので、任意の波形データを別の任意の波形データへの相互変換が可能です。

# 強力なスクリプト言語

WaveFormerProはPerl言語 (Practical Extraction and Report Language)をもとにした強力なスクリプト言語(Waveperl)を持ちます. WaveFormerProのあらゆる有用なAPIが公開されており、スクリプト・プログラミングを通して適切に引用することにより、任意の波形フォーマットのWaveFormerProへの読み込み、 WaveFormerProからの任意のフォーマットへの書き出し、複雑な波形の生成、編集機能の強化ができます. これによりユーザの環境に必要な形にWaveFormerProをカスタマイズできます.

# 広い用途

WaveFormerProは設計の多くの局面で使用できるEDAツールですが,設計のみならずドキュメント参照ツールとしてテスト,保守,修理にいたるまで,共有の必要な波形という情報を管理するソフトウェアでもあります. WaveFormerProにより,同じ商品に関わるだれもが,それぞれの立場で波形に関する問題を解決するために必要な情報の共有がたやすくできる,地味ながら設計以外の所でも利用価値の高いツールです.

# タイミング・ライブラリ

付属のタイミング・ライブラリを使うことで、一覧からのデバイスとパラメータの選択だけでタイミング解析ができます、

標準ロジック・デバイス・ライブラリ 80x86ライブラリ

# システム条件

300MHz以上のCPU

Microsoft Windows95/98/Me, NT, 2000のいずれかが走行している環境.

64Mバイト以上のメモリ

50Mバイト以上のハードディスクの空き

# WaveFormerPro に組み合わせ可能な他のツール

WaveFormerProに組み合わせて使うことにより、ワークステーションクラスの性能と機能にひってきする環境を、従来にない価格で築けます、全てWindows98/Me/NT40/2000/XPで走行するソフトウエアです。

### CoDeveloper

ハード・ソフト強調C言語設計の決定版。

定評のある米国ロスアラモス国立研究所のStreams Cの商品化。

標準のANSI Cでの設計で、特別な拡張言語は使用せず、判りやすく安価。

HDS (Chip Designer, Board Designer, System Designer)

回路図(ブロック図)からVHDLやVerilog-HDLのネットリストを生成するブロック・エディタの機能を有する汎用回路 図エディタで,OEMやソース・ライセンスで多く使われているHDL設計での標準品.他のツールを登録しランチン グする機能,公開APIで他のツールをインテグレートできるなど,フレームワーク的な使用が可能.

#### **SMASH**

Spice, VHDL, Verilog, C, VHDL-AMSを自由に組み合わせてシステム記述をしてシミュレーションの実行ができます. A/D mix やSoCの開発に最適です。またBsim3などのトランジスタ・モデルを持ち、IC開発のためのSpiceシミュレータとしても活用できます。

### MasterClass

CD-ROMのマルチメディアVHDLトレーニングソフト(英語)であり、VHDLの難解な部分を楽しく大変にやさしく説明、VHDLのオンラインリファレンスの機能もあり、設計時にVHDLのシンタックスの参照をその場でできる。

インターラクティブ Verilogシミュレータとしての応用についてはこの資料では記述されていません。

上位互換商品 TestBencher Pro もあります。

下記へお問い合わせ下さい

# InterLink(有)インターリンク

〒231-0023 神奈川県横浜市中区山下町252 グランベル横浜9F Phone: (045) 663-5940 FAX: (045)663-5945 e-mail: ilink\_sales@ilink.co.jp ilink\_support@ilink.co.jp http://www.ilink.co.jp

©1996 SynaptiCAD, Inc. All rights reserved.

Microsoft and Windows are registered trademarks and Windows NT is a trademark of Microsoft Corp.

Synario and Data IO are registered trademarks of DATA I/O Corporation. Viewlogic is a registered trademark of Viewlogic Corporation. StateCAD is a trademark of Visual Software Solutions, Inc.

Verilog is a registered trademark of Cadence Design Systems, Inc.

Other product or brand names mentioned are property of their respective holders.