昡壙斉傪偛婓朷偝傟傞偍媞條偼丄壓婰偺楢棈愭傊偍栤偄崌傢偣壓偝偄丅

亂偍栤偄崌傢偣愭亃

傾僀儕儞僋

仹231-0023

墶昹巗拞嬫嶳壓挰256

償傿儖僰乕僽墶昹娭撪丂侾奒111

TEL丗045-663-5940

FAX丗045-663-5945

email丗

塩嬈 ilink_sales@ilink.co.jp

媄弍 ilink_support@ilink.co.jp

CoDeveloper(Impulse C)

Hardware Generation

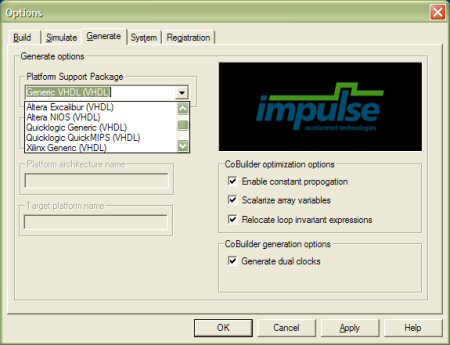

CoMonitor僔儈儏儗乕僔儑儞偱摦嶌妋擣偝傟丄愝寁傪僴乕僪僂僃傾乮FPGA乯偵幚憰偡傞弨旛偑偱偒偨傜丄僴乕僪壔偡傞僾儘僙僗傪寛掕偟僞乕僎僢僩FPGA傪慖戰偟傑偡丅CoBuilder偑摦嶌崌惉傪幚峴偟丄懳徾僾儘僙僗偼僞乕僎僢僩偵嵟揔壔偝傟偨VHDL僐乕僪偵曄姺偝傟傑偡丅丂

仭Code generation options偵傛傝丄懳徾FPGA傊偺CoBuilder弌椡偺挷惍 偑偱偒傑偡丅

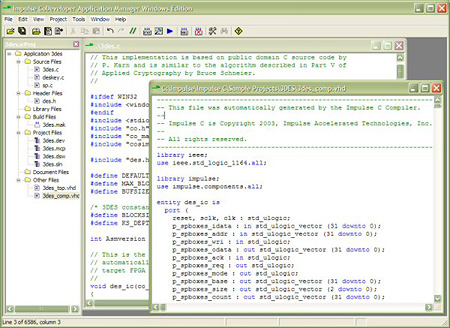

CoBuilder 偼丄僐儞僷僀儖偵愭棫偪丄奺僾儘僙僗傪夝愅偟偰掅悈弨偺暲峴摦嶌傪摫擖偱偒傞婰弎傪尒偮偗丄摦嶌傪僗働僕儏乕儖偟偰僷僀僾儔僀儞壔傪帋傒傑偡丅 偦偟偰丄堦斒偺VHDL榑棟崌惉僣乕儖偱崌惉壜擻偺RTL悈弨偺VHDL僐乕僪傪弌椡偟傑偡丅弌椡僐乕僪偼丄慖戰偝傟偨FPGA僼傽儈儕乕偵嵟揔壔偝傟偨丄僜僼僩僂僃傾丒僾儘僙僗偲僾儘僙僗娫捠怣乮僗僩儕乕儉丒僶僢僼傽丄僔僌僫儖丄嫟桳儊儌儕乯偱偒傞僀儞僞乕僼僃乕僗丒儘僕僢僋傪娷傓傕偺偱偡丅

仭惗惉偝傟傞VHDL僐乕僪偼丄昗弨揑側榑棟崌惉僣乕儖傗僔儈儏儗乕僞偲屳姺偱偡丅

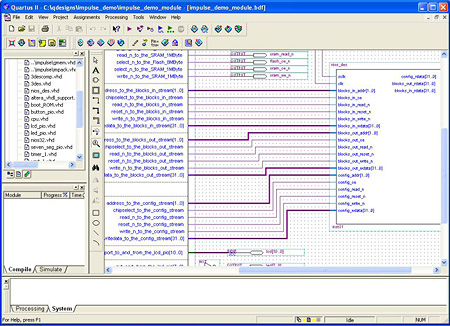

RTL VHDL僐乕僪偑摼傜傟昁梫偵墳偠偰VHDL僔儈儏儗乕僔儑儞乮昗弨揑側IEEE弨嫆VHDL僔儈儏儗乕僞偐Impulse幮偺CoValidator乯偱摦嶌妋擣傪偟丄 偦偺屻偺FPGA偵幚憰偡傞夁掱偼丄懳徾FPGA傪僒億乕僩偡傞昗弨偺FPGA儀儞僟乕丒僣乕儖偱壜擻偱偡丅椺偊偽丄Altera幮偺 Quartus嘦偵傛傝丄CoBuilder偵傛傝惗惉偝傟偨VHDL僐乕僪偼榑棟崌惉丄嵟揔壔丄攝抲攝慄偝傟Altera Cyclone僠僢僾側偳偵幚憰偱偒傑偡丅埲壓偼丄Altera Quartus嘦偵傛傞幚椺偱偡丅

仭CoDeveloper偺僀儞僞乕僼僃乕僗丒儔僀僽儔儕偼丄Impulse C偺僴乕僪僂僃傾丒僾儘僙僗偲ImpulseC偺僜僼僩僂僃傾丒僾儘僙僗乮僜僼僩CPU丗Nios側偳乯傪帺摦愙懕